# LIBRARY OF THE UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

510.84 Il Gr mo.433-438 cop. 2

http://archive.org/details/illiaciiireferen434mcco

-

· · ·

510.07 ILGN no.43f

Report No. 434

Mach

000-2118-0006

ILLIAC III REFERENCE MANUAL VOLUME II: Instruction Repertoire

edited by B. H. McCormick and B. J. Nordmann, Jr.

THE LIBRARY OF THE

MAY 1 8 1971

D. E. Atkins, R. T. Borovec, L. N. Goyal, L. M. Katoh, R. M. Lansford, J. C. Schwebel and V. G. Tareski UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

February 26, 1971

DEPARTMENT OF COMPUTER SCIENCE UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN · URBANA, ILLINOIS

# 000-2118-0006

Report No. 434

### ILLIAC III REFERENCE MANUAL

VOLUME II: Instruction Repertoire

edited by

B. H. McCormick and B. J. Nordmann, Jr.

D. E. Atkins, R. T. Borovec, L. N. Goyal, L. M. Katoh, R. M. Lansford, J. C. Schwebel and V. G. Tareski

February 26, 1971

Department of Computer Science University of Illinois Urbana, Illinois 61801

This work was supported by Contract AT(ll-l)-lol8 with the U.S. Atomic Energy Commission through September 30, 1970. Current support is under Contract AT(ll-l)-2118 with the above agency.

#### ABSTRACT

The Illiac III Reference Manual is being issued in this final documentation as four volumes:

Volume I; The Computer System This issue---Volume II: Instruction Repertoire Volume III; Input/Output Volume IV: Supervisor Organization

For ease of cross-reference an integrated table of contents will be issued separately.

This section (Volume II) deals with the extraordinarily diverse instruction repertoire of the Illinois Pattern Recognition Computer (Illiac III). As the "central processing units" of the machine, a Taxicrinic Processor interprets these instructions and, if appropriate, routes the relevant operands and control information to units of the machine for execution: to the main store, arithmetic unit, pattern articulation unit, and interrupt unit. Indirectly, by mediation of the interrupt unit, the Taxicrinic Processor can also initiate and terminate I/O operations.

Certain novel aspects of the instruction repertoire are reiterated here. First, the Taxicrinic Processors interpret the unique instructions to control plane parallel picture processing in the Pattern Articulation Unit. (See Section 2.4) Secondly, because the latter phases of image analysis so commonly involves graph transformations, the machine code emphasizes a set of list processing instructions. Again to permit ready implementation of list processing and graph transformation languages, the imprimitive instructions are introduced in Section 2.2.10. These provide the basis for a hardware-implemented macro-assembler, and allow for efficient use of interpretive realizations of programming languages.

Finally it should be noted that the instruction repertoire, particularly in the so-called "system instructions", Section 2.2.11, takes full cognizance of the special problems facing an operating system coordinating multiple processors in a multi-programming environment.

#### ACKNOWLEDGMENTS

The Illiac III Reference Manual is based in part upon two earlier reports:

- B.H. McCormick (editor), William D. Bond, Kimio Ibuki, Roger

E. Wiegel and John A. Wilber, Preliminary Programming Manual for the Illiac III Computer, Department of Computer Science Report 185, University of Illinois, July 1965.

- B.H. McCormick and R.M. Lansford (editors), D.E. Atkins, R.T. Borovec, G.N. Cederquist, S.K.Chan, L.A. Dunn, J.P. Hayes, L.M. Katoh, P.L. Koo, B.J. Nordmann, Jr., J.A. Rohr, and J.C. Schwebel, <u>Illiac III Programming Manual</u>, Department of Computer. Science Manual, University of Illinois, March 1968.

The present editors (B.H. McCormick and B.J. Nordmann, Jr.) acknowledge with gratitude the contribution of these earlier groups as transplanted to this greatly expanded manual. In addition, Dr. Rangaswamy Narasimhan contributed significantly to the early definition of the pattern articulation unit instruction set. In like manner Philip Merryman assisted materially in the early formulation of machine-implemented macros--the imprimitive instructions of Illiac III.

Authors and contributors to the manual are listed by principal area of concern:

| Taxicrinic Processor:      | B.J. Nordmann, Jr., R.M. Lansford,<br>J.C. Schwebel, R.E. Wiegel     |

|----------------------------|----------------------------------------------------------------------|

| Input/Output Processor:    | L.M. Katoh, V.G. Tareski, J.V. Wenta,<br>G.N. Cederquist, J.P. Hayes |

| Arithmetic Units:          | D.E. Atkins, L.M. Goyal                                              |

| Pattern Articulation Unit: | R.T. Borovec, R.P. Harms, G.T. Lewis                                 |

| Interrupt Unit:            | L.M. Goyal                                                           |

| Exchange Net:              | S.K. Chan, P. Krabbe                                                 |

| Scanner-Monitor-Video      | L.A. Dunn, L.M. Goyal, V.G. Tareski,<br>R.G. Martin, R.C. Amendola   |

| Supervisor Organization:   | B.J. Nordmann, Jr., R. M. Lansford                                   |

The seemingly endless drafts and revisions of this manual have been handled with patience and fortitude by Mrs. Betty Gunsalus and Mrs. Roberta Andre'. Illustrations were prepared by Mr. Stanley Zundo.

## 2. INSTRUCTION REPERTOIRE

- 2.1 Instruction Format

- 2.1.1 Mnemonic Byte

- 2.1.2 Operand Phrases

- 2.1.2.1 Tag Field (TAG)

- 2.1.2.2 Slash Operation Field  $(S\emptyset)$

- 2.1.2.3 Indirect Bit (I)

- 2.1.2.4 Last Bit (L)

- 2.1.2.5 Flag Bit (F)

- 2.1.2.6 Modifier Field (M<sub>0</sub>, M<sub>1</sub>)

- 2.1.2.7 Modification Operation Bits  $(m_0, m_1)$

- 2.1.2.8 Sequence of Operations for Operand Phrases

- 2.2 Instructions Executed by the Taxicrinic Processor

- 2.2.1 Single Cycle Data Transfers

- 2.2.1.1 Assign

- 2.2.1.2 Operand Stack Instructions

- 2.2.1.2.1 Push

- 2.2.1.2.2 Pop

- 2.2.1.2.3 Load

- 2.2.1.2.4 Store

- 2.2.1.3 Masked Operations

- 2.2.1.3.1 Set

- 2.2.1.3.2 Reset

- 2.2.1.3.3 Test

- 2.2.1.3.4 Test with Mask

- 2.2.2 Multiple Cycle Data Transfers

- 2.2.2.1 Operand Stack Field Transfers

- 2.2.2.1.1 Push Field

- 2.2.2.1.2 Push Field Reverse

- 2.2.2.1.3 Pop Field

- 2.2.2.1.4 Pop Field Reverse

- 2.2.2.1.5 Pointer Manipulation

- 2.2.2.2 Field Comparison

- 2.2.2.2.1 Scan

- 2.2.2.2 Scan with Mask

- 2.2.2.3 Decimal Conversion 2.2.2.3.1 Pack Numeric

- 2.2.3.2 Unpack Numeric

2.2.2.4 String Manipulation 2.2.2.4.1 Move 2.2.2.4.2 Translate 2.2.2.4.3 Edit 2.2.3 Stack Utility 2.2.3.1 Exchange 2.2.3.2 Duplicate 2.2.3.3 Sluff 2.2.4 Logical Operations 2.2.4.1 Unary Logical 2.2.4.1.1 Zero 2.2.4.1.2 One 2.2.4.1.3 Not 2.2.4.1.4 Count Ønes 2.2.4.1.5 Bit 2.2.4.2 Binary Logical 2.2.4.2.1 And 2.2.4.2.2 Or 2.2.4.2.3 Exclusive Or 2.2.4.2.4 Equivalence 2.2.4.2.5 Compare Logically 2.2.5 Shift 2.2.5.1 Left Shift 2.2.5.2 Right Shift 2.2.6 Conditional Instructions 2.2.6.1 If 2.2.6.2 If Not 2.2.7 Utility 2.2.7.1 Location 2.2.7.2 Specify 2.2.7.3 No Operation 2.2.8 Arithmetic Operations 2.2.8.1 Unary Arithmetic 2.2.8.1.1 Negate 2.2.8.1.2 Absolute Value 2.2.8.1.3 Minus 2.2.8.1.4 Test Algebraically 2.2.8.1.5 Convert Short to Long Fixed Point

2.2.8.2 Binary Arithmetic

2.2.8.2.1 Fixed Point Addition

2.2.8.2.2 Fixed Point Subtraction

2.2.8.2.3 Fixed Point Algebraic Comparison

- 2.2.9 List Processing Instructions

- 2.2.9.1 Sequence Left

- 2.2.9.2 Sequence Right

- 2.2.9.3 Get Cell

- 2.2.9.4 Put Cell

- 2.2.9.5 Insert Cell Left

- 2.2.9.6 Insert Cell Right

- 2.2.9.7 Delete Cell Left

- 2.2.9.8 Delete Cell Right

- 2.2.10 Imprimitive Instructions

- 2.2.10.1 Operational Description

- 2.2.10.2 Go To

- 2.2.10.3 Execute

- 2.2.10.4 Call

- 2.2.10.5 Exit

- 2.2.10.6 Name Permutation and Repermutation

- 2.2.11 System Instructions

2.2.11.1 Supervisor Operation 2.2.11.1.1 Supervisor Call 2.2.11.1.2 Supervisor Return 2.2.11.1.3 Rename 2.2.11.1.4 Sleep 2.2.11.1.5 Activate TP 2.2.11.1.6 Reserve Unit 2.2.11.1.6 Reserve Unit 2.2.11.1.7 Load Task Register 2.2.11.1.8 Store Task Registers 2.2.11.2.1 Set Interrupt Mask 2.2.11.2.1 Set Interrupt Mask 2.2.11.2.2 Interrupt Return

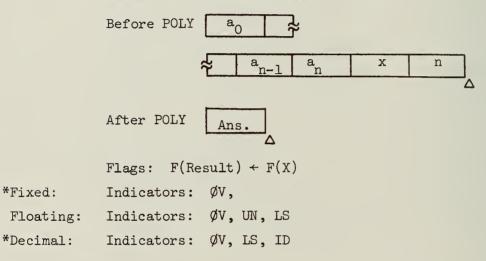

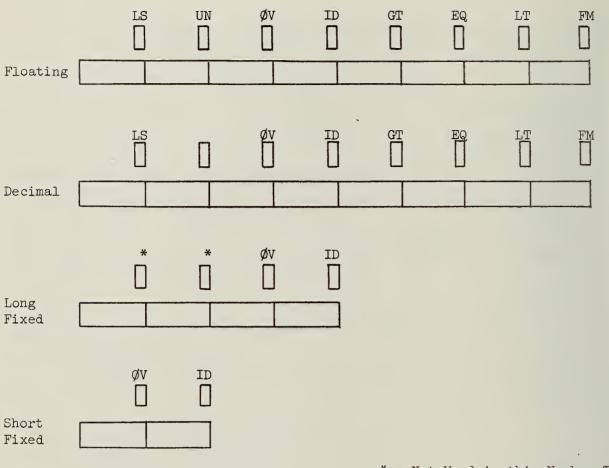

2.2.11.3 Input/Output 2.2.11.3.1 Start I/0 2.2.11.3.2 Halt I/0 2.2.11.3.3 Load IOP Base Register 2.2.11.4 Coordination 2.2.11.4.1 Increment and Check 2.2.11.4.2 Link 2.2.11.4.3 Who 2.2.11.5 Timing 2.2.11.5.1 Read Clock 2.2.11.5.2 Set Timer 2.2.11.5.3 Read Timer 2.3 Instructions Executed by Arithmetic Units 2.3.1 Arithmetic Data Formats 2.3.1.1 Short Fixed Point 2.3.1.2 Long Fixed Point 2.3.1.3 Floating Point 2.3.1.4 Decimal 2.3.2 Arithmetic Instructions 2.3.2.1 Add 2.3.2.2 Subtract 2.3.2.3 Multiply 2.3.2.4 Divide 2.3.2.5 Compare Algebraically 2.3.2.6 Convert to Decimal 2.3.2.7 Convert to Floating Point 2.3.2.8 Convert to Long Fixed Point 2.3.2.9 Polynomial Evaluation 2.3.3 Exceptional Conditions for Arithmetic Instructions 2.3.3.1 General 2.3.3.2 Overflow (OV) 2.3.3.3 Underflow (UN) 2.3.3.4 Invalid Decimal Data (ID) 2.3.3.5 Loss of Significance (LS)

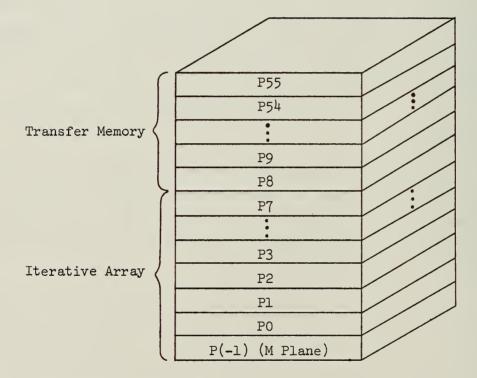

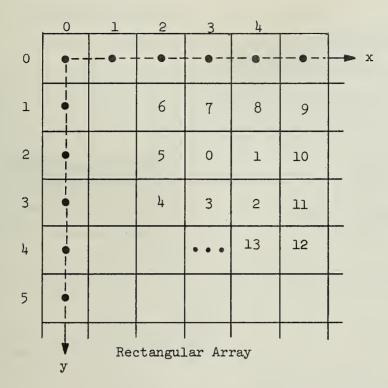

'2.4 Instructions Executed by the Pattern Articulation Unit 2.4.1 Conventions 2.4.1.1 Planes and Borders 2.4.1.2 Direction Numbers 2.4.1.3 Indicators 2.4.1.3.1 Exceptional Conditions 2.4.1.3.2 Indicator Halfword 2.4.2 Zero-Plane Instructions 2.4.2.1 Topology 2.4.2.2 Set Origin 2.4.2.3 Resume 2.4.2.4 Restart 2.4.3 One-Plane Instructions 2.4.3.1 Data Formats 2.4.3.1.1 Coordinate Mode 2.4.3.1.2 Incremental Code 2.4.3.2 Clearp 2.4.3.3 Setp 2.4.3.4 Testp 2.4.3.5 Testb 2.4.3.6 Replicate 2.4.3.7 Shift 2.4.3.8 Tally 2.4.3.9 Tallyho 2.4.3.10 Area 2.4.3.11 List 2.4.3.12 Listsz 2.4.3.13 List1z 2.4.3.14 Listi 2.4.3.15 Readlz 2.4.3.16 Rderlz 2.4.3.17 Erasep 2.4.3.18 Plot 2.4.3.19 Plotsz 2.4.3.20 Plot1z

2.4.3.21 Ploti 2.4.3.22 Writlz 2.4.3.23 Wrerlz

- 2.4.4 Two-Plane Instructions

- 2.4.4.1 Copy

- 2.4.4.2 Copyc

- 2.4.4.3 Pland

- 2.4.4.4 Plor

- 2.4.4.5 Plnand

- 2.4.4.6 Plnor

- 2.4.4.7 Plexor

- 2.4.4.8 Pleqv

- 2.4.5 Three-Plane Instructions

- 2.4.5.1 Connect

- 2.4.6 Multiple-Plane Instructions

2.4.6.1 Boole

2.4.6.2 Gate IA

- 2.4.7 Border Instructions

- 2.4.7.1 Data Formats

2.4.7.1.1 Raster String 2.4.7.1.2 GBW Byte

- 2.4.7.2 Loadb

- 2.4.7.3 Storeb

- 2.4.7.4 Pushb

- 2.4.7.5 Popb

- 2.4.7.6 Moveb

- 2.4.8 Information on Boole Instruction

2.4.8.1 Availability List

2.4.8.2 Form for Specifying General Boolean Functions

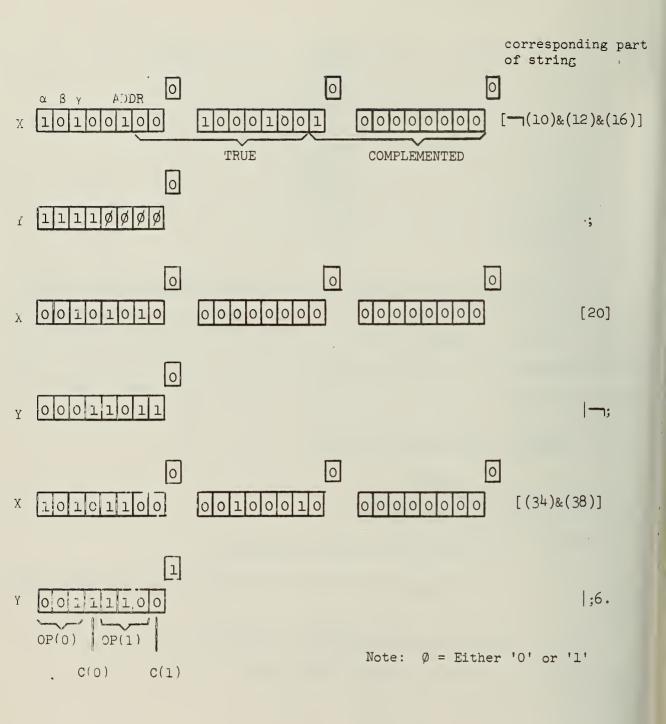

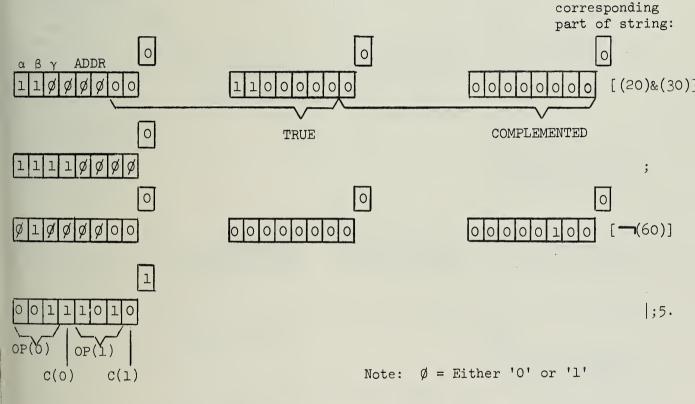

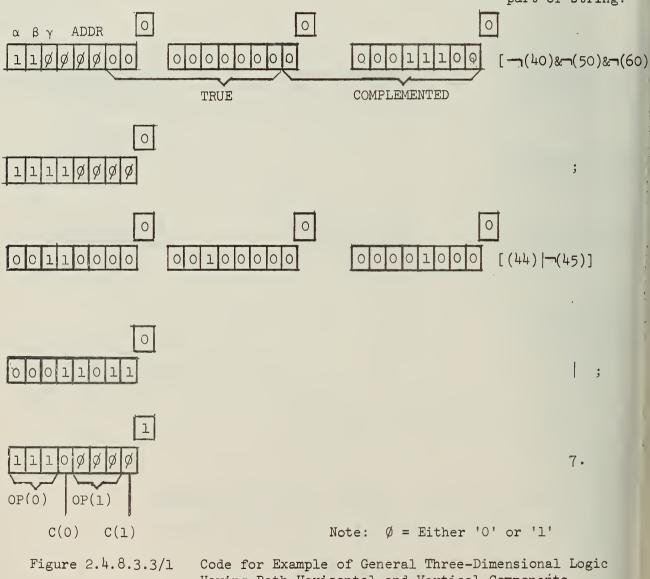

2.4.8.3 Examples Illustrating the Coding

2.4.8.3.1 Purely Horizontal Logic

2.4.8.3.2 Purely Vertical Logic

2.4.8.3.3 General Three-Dimensional Logic

#### 2. INSTRUCTION REPERTOIRE

This section (Volume II) deals with the extraordinarily diverse instruction repertoire of the Illinois Pattern Recognition Computer (Illiac III). As the "central processing units" of the machine, a Taxicrinic Processor interprets these instructions and, if appropriate, routes the relevant operands and control information to units of the machine for execution: to the main store, arithmetic unit, pattern articulation unit, and interrupt unit. Indirectly, by mediation of the interrupt unit, the Taxicrinic Processor can also initiate and terminate I/O operations.

Certain novel aspects of the instruction repertoire are reiterated here. First, the Taxicrinic Processors interpret the unique instructions to control plane parallel picture processing in the Pattern Articulation Unit. (See Section 2.4) Secondly, because the latter phases of image analysis so commonly involves graph transformations, the machine code emphasizes a set of list processing instructions. Again to permit ready implementation of list processing and graph transformation languages, the imprimitive instructions are introduced in Section 2.2.10. These provide the basis for a hardware-implemented macro-assembler, and allow for efficient use of interpretive realizations of programming languages.

Finally it should be noted that the instruction repertoire, particularly in the so-called "system instructions", Section 2.2.11, takes full cognizance of the special problems facing an operating system coordinating multiple processors in a multi-programming environment.

Section 2-1/1

2/25/71

#### 2.1 Instruction Format

Every Illiac III instruction can be considered to be in prefix form: an operation (specified by a mnemonic byte)followed by operands (designated by operand phrases), if any. An instruction with n operands in main storage has n operand phrases respectively, each one implicitly specifying the data address of the operand. In addition, an instruction may call upon operands from the Operand Stack. In this case, the operand address is implied by the mnemonic byte.

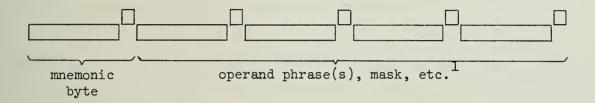

The general format for the Illiac III instructions is shown in figure 2.1.

Figure 2.1 Illiac III Instruction Format

This format consists of a single mnemonic byte normally followed by one or more operand phrases. These phrases may be long or short(see Section 2.1.2).

In primitive instructions the total length of these operand phrases may not exceed 4 bytes. Some few primitive instructions, while adhering to the 4-byte constraint, have fields with alternate interpretation: mask, etc.

In imprimitive instructions there may be up to 12 operand phrases. Here however, no restriction is placed upon the total length of the instruction.

<sup>1</sup> For imprimitive instructions up to 12 operand phrases are allowed (36 bytes max.).

#### 2.1.1 Mnemonic Byte

Every instruction is defined and initiated by a single mnemonic byte. The mnemonic byte may alone define the instruction or it may have associated with it one or more operand phrases and/or an auxiliary condition mask.

The instructions are partitioned into eight classes by three fixed bits of the mnemonic byte (specifically, by the first 2 prefix bits and the flag bit). Some of these classes correspond to familiar programming instruction sets: arithmetic, pattern articulation, etc. Others designate the number of associated operands: zero, one, two (for primitives) or arbitrary (for imprimatives).

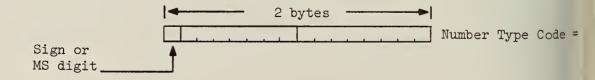

The two low order data bits of the mnemonic byte are often reserved for the Field Designator (FD) or the Number Type (NT). This latter situation is peculiar to arithmetic instructions and is discussed separately in Section 2.3.

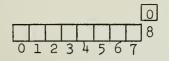

The Field Designator (FD) is the operand field length (1, 2, 4 or 8 bytes) if the operand phrase(s) refer to a core address. If the operand phrase(s) refer to a Pointer Register, these bits indicate the pointer field to be used, i.e. Link, Value, Segment Name or appropriate combination thereof.

If the Immediate option was not specified by the (either) operand phrase, the fields designated are used to refer to a core or stack field; all flags of each field are transmitted.

| 00 | Byte                  |

|----|-----------------------|

| 01 | Halfword              |

| 10 | Word (4 bytes)        |

| 11 | Double word (8 bytes) |

Section 2.1.1 - 1/2

7/27/70

If the (either) operand phrase specifies the Immediate option, the fields then designated are used to refer to program register fields.

| 00 | Value (no flags, halfword)        |

|----|-----------------------------------|

| Ol | Link (no flags, halfword)         |

| 10 | Link and Value (all flags, word)  |

| 11 | Segment Name (no flags, halfword) |

Not all instructions permit the Immediate option; see instruction text where in doubt.

#### 2.1.2 Operand Phrases

Operand phrases provide a uniform technique throughout Illiac III for addressing main storage and for operating on the 15 pointer stacks. In an operand phrase, the file (main store) address of an operand is implied by giving the name of its associated pointer stack. That is, the data address is specified by the topmost pointer in the pointer stack named by the operand phrase tag field.

In addition to naming a pointer stack, an operand phrase may also specify operations which modify the value of the pointer and/or change the depth of the pointer stack. These operations take place before, after, or both before and after the actual execution of the kernel instruction.

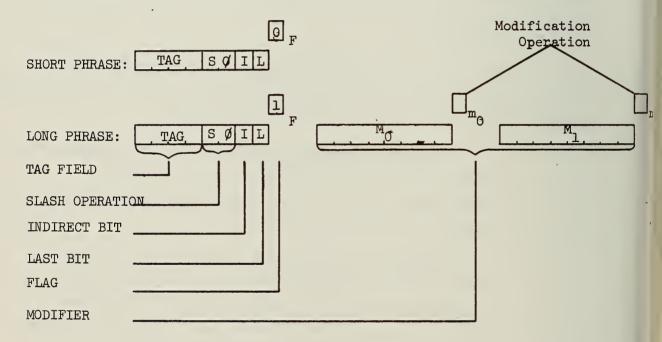

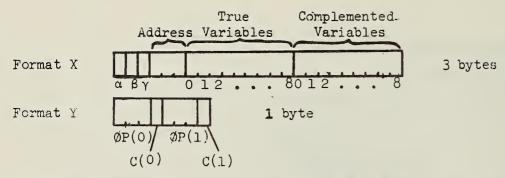

The length of each <u>operand phrase</u> (1 or 3 bytes) is specified by the flag of the first byte of each phrase: a flag of '0' indicates a short phrase; a flag of '1' indicates a long phrase.

> For <u>primitive instructions</u> a maximum of two operand phrases (only one of which can be long) is allowed. Additional single byte fields may be intermingled if prescribed by the instruction format.

For <u>imprimitive instructions</u> a maximum of 14 operand phrases (long or short) is permitted. No other fields may be intermingled. The terminal phrase is specified by the low order data bit of the first byte of the operand phrase: '0' if more phrases follow, '1' for the terminal phrase.

Accordingly the instruction field is consecutively partitioned into phrases until (a) the number of phrases specified by the mnemonic byte is exhausted (**primitives**), or (b) a terminal bit is sensed (imprimitives). Every operand, other than those in the top of the Operand Stack, is designated by the use of an Operand Phrase.

Every operand phrase has one of two forms: a single=byte short phrase or a three-byte long phrase. A <u>short</u> phrase is indicated when the flag bit of the first byte is '0'; a <u>long</u> phrase is indicated when this bit is 'l'.

The fields of the two types of operand phrases are shown in Figure 2.1.2.

7/6/70

Section 2.1.2 - 2/2

## 2.1.2.1 Tag Field (TAG)

The first 4 bits of the first byte of the operand phrase is the tag field. This field designates, or names, one of the 15 pointer registers which is to be operated, on renamed, or otherwise employed in the construction of the operand address.

In a Taxicrinic Processor there are 15 pointer registers, each having an associated 4-bit name register. As implied, the name register holds the current name (e.g., PR<sub>3</sub>) of the pointer register. At any given time each pointer register must have a unique name, i.e., no two name registers may contain the same name.

When an <u>imprimitive instruction</u> is executed, some or all of the names of the pointer registers may be permuted, i.e., some or all of the name registers may be changed, but after name permutation each pointer register will still have a unique name. For the CALL and EXECUTE imprimitive instructions the new name is specified by the position of the phrase and its tag: the tag of the operator phrase specifies which pointer register may be renamed  $PR_0$ ; the tag of the next operand phrase specifies which pointer register may be renamed  $PR_1$ ; the tag of the third operand phrase specifies which pointer register may be renamed  $PR_2$ ; etc. If there are less than 15 operand phrases the remaining pointer register names are automatically permuted as described below in Section 2.2.10.6.

For the CALL and EXECUTE imprimitive instructions, name changing consists of possibly permuting every pointer register name. For the GØTØ imprimitive instruction, name changing consists only of possibly swapping the names of  $PR_0$  and the pointer register designated by the tag field of the operator phrase. For any imprimitive instruction the appropriate type of name change (permutation or swapping) <u>will</u> occur unless a conditional subtraction failure occurs for some modification as described below in Section 2.2.10.3. For <u>imprimitive</u> instructions two special conventions are adhered to:

Because of its importance for <u>imprimitive</u> instructions, the first such operand phrase, should it exist, will be designated as the <u>operator</u> phrase. The function of the operator phrase is to control the instruction pointer,  $PR_0$ , and thus control program flow. The format of the operator phrase is the same as for a general operand phrase, except for a minor restriction: the SØ field is ignored.

In every <u>imprimitive</u> operand phrase, the last data bit of the first byte is a Last bit (L). If L = '0', more operand phrases follow; if L = 'l', this is the terminal (i.e., last) operand phrase of the instruction.

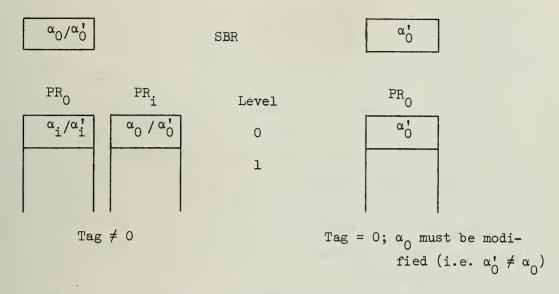

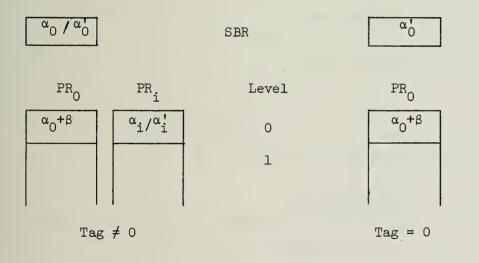

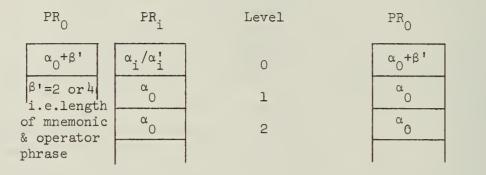

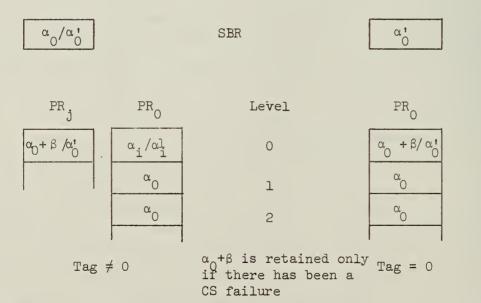

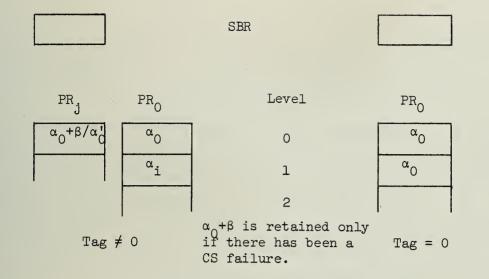

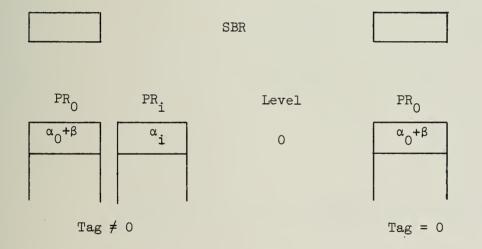

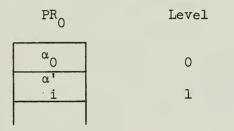

For imprimitive instructions only, then, the tag field of the operator phrase specifies which pointer register may be renamed  $PR_0$ . If the tag of the operator phrase is 0, the current instruction pointer register is modified as specified by the modifier of the phrase. If the tag of the operator phrase is not zero, the specified pointer is modified by the modifier of the operator phrase, and then that pointer may be renamed  $PR_0$ .

#### 2.1.2.2 Slash Operation Field (SØ)

The slash operations control the "pushing" and "popping" of the designated pointer stack. The first bit of the slash operation,  $S\emptyset_0$  is called the <u>pre-slash</u> and, if set to 'l', indicates that the pointer stack is to be duplicated (pushed) before executing the instruction. Bit  $S\emptyset_1$  is called the <u>post-slash</u>, and if set to 'l', indicates that the pointer stack is to be popped after execution of the instruction. The following table gives the interpretation of the four possible variants:

| Pre-Slash Bit | Post-Slash Bit | Operand Operation  | Initial/Final Operation |        |  |

|---------------|----------------|--------------------|-------------------------|--------|--|

| 0             | 0              | FINAL VALUE        | no push                 | no pop |  |

| 0             | 1              | POP ON EXIT        | no push                 | рор    |  |

| l             | 0              | SAVE INITIAL VALUE | push                    | no pop |  |

| 1             | 1              | INITIAL VALUE      | push                    | рор    |  |

The interpretation expresses the status of the pointer of the named operand file upon completion of the instruction.

Note: For imprimitive instructions the slash operations specified for an <u>operator</u> phrase will be <u>ignored</u>; they are implied by the nmemonic byte.

Section 2.1.2.2 - 1/1

#### 2.1.2.3 Indirect Bit (I)

The interpretation of this bit depends on whether the phrase is short or long. If the phrase is short, this bit is used to specify Indirect addressing. If the phrase is long, this bit is used to specify an Indirect Modifier.

> <u>Indirect Addressing</u>: If the phrase is short, the indirect bit designates whether the effective operand address is computed directly (I=0) or indirectly (I=1) from the specified pointer register. If indirect addressing is specified, the pointer register specified by the tag of the phrase is used to access a halfword in core (flag bits excluded). This halfword then <u>replaces</u> the value of the pointer register specified by the short phrase.

<u>Indirect Modifier</u>: If the phrase is long, this bit designates whether the Modifier Field  $(M_0, M_1)$  contains the modifier itself (I=0) or whether the Modifier points to a pointer register (or  $\emptyset$ S) which contains the modifier (I=1).

#### 2.1.2.4 Last Bit (L)

The last data bit of the first byte of an instruction operand phrase has one of four interpretations depending on the instruction.

Last Bit (L): In every imprimitive operand phrase, if L = '0', more operand phrases follow; if L = 'l', this is the terminal (i.e., last) operand phrase of the instruction.

<u>Count Phrase Bit (Ct</u>): If the primitive instruction requires a count, e.g. Push Field, then the first operand phrase is a count phrase. If Ct = 'l', then the pointer value specified by the tag is used as the count; if Ct = '0', no count exists and a flag on the data is used to terminate the instruction.

<u>Immediate Operand Bit (Imm</u>): Some primitive instructions allow the possibility of using a pointer register (or some portion of it) as an immediate operand rather than as the address of an operand. If Imm = '0', the pointer will be used as an address. For those instructions which allow Immediate operands, if Imm = '1', the Field Designator bits (FD) will be interpreted as follows:

- 00 Value field: right half of the PR, no flags

- Ol Link field: left half of the PR, no flags

- 10 Register: all of the PR, including flags

- 11 Segment Name field: Segment Name Register corresponding to PR, no flags.

The instruction then applies to these fields of the pointer specified by the tag of the phrase.

Note: Operand phrases which may have immediate operands (count) are marked in this manual with an Imm (Ct) as a superscript immediately following the phrase.

<u>Unused</u>: For many primitive instructions the last data bit of the first byte of an operand is unused.

# 2.1.2.5 Flag Bit (F)

The flag bit always indicates whether the phrase is long or short. For all operator/operand phrases if the flag bit is '0', the phrase is short; if the flag bit is 'l' the phrase is long and the next two bytes specify a modifier to be applied to the pointer register (value).

# 2.1.2.6 Modifier Field (M<sub>0</sub>, M<sub>1</sub>)

A modifier field occurs only for a long phrase and consists of the data bits of the second and third bytes of the phrase denoted by  $M_0$  and  $M_1$ .

If the Indirect bit (I) = '0', the modifier is used directly as specified by the Modification Operation Bits  $m_0$  and  $m_1$ . The modifier value M is considered to be a 16-bit positive integer.

If the Indirect bit = 'l', the leftmost four bits of  $M_0$  are used to specify a Secondary Tag. The pointer <u>value</u> of the specified secondary register is applied to the primary register as specified by the Modification Operation Bits  $m_0$  and  $m_1$ . The secondary tag may specify  $PR_0$ , ...,  $PR_{15}$ .  $PR_{15}$  is interpreted to mean that the Indirect Modifier is to be taken from the top halfword cell in the  $\emptyset$ S. The contents of the secondary register (or  $\emptyset$ S) are not changed by this process. 2.1.2.7 Modification Operation Bits  $(m_0, m_1)$

The modification operation bits, (the flag bits on the second and third bytes of a long operand phrase) denoted  $m_0$  and  $m_1$ , are used to specify the operation to be performed on the pointer value after the pre-slash operation (if any). The four possible operations are specified in the table below.

| <sup>m</sup> o | ml | Operation               | Symbol |  |  |

|----------------|----|-------------------------|--------|--|--|

| 0              | 0  | REPLACEMENT             | =      |  |  |

| 0              | l  | ADDITION                | +      |  |  |

| l              | 0  | CONDITIONAL SUBTRACTION | -      |  |  |

| l              | 1  | NOT USED                |        |  |  |

REPLACEMENT causes the modifier M(or if Indirectly Modified, the Secondary Pointer value) to replace the pointer value specified by the tag of the phrase <u>before</u> execution of the instruction.

CONDITIONAL SUBTRACTION causes calculation of a test value by subtracting the modifier M (or if Indirectly Modified, the Secondary Pointer value) from the pointer value specified by the tag ( both treated as positive 16-bit integers) <u>before</u> execution of the instruction.

ADDITION causes the modifier M (or if Indirectly Modified, the Secondary Pointer value) to be added, modulo 2<sup>16</sup> to the pointer value specified by the tag of the phrase <u>before</u> execution of the instruction. Note: <u>If the tag of a phrase is zero, the addition is done</u> on the address of the first byte of the instruction; and a transfer of control will occur prior to the execution of the next instruction.

If the test value is greater than zero, the test value replaces the specified pointer value and instruction processing continues. If the test value is less than or equal to zero, the specified pointer value is not modified. Then after all operand phrases have been processed, if a conditional subtraction has been attempted, the Conditional Subtraction indicator (CS) is reset to the outcome of the 'OR' of any (possibly multiple) attempted conditional subtractions.

If any conditional subtraction has failed, the instruction is not executed, and any modifications performed on  $PR_0$  are cancelled. Execution continues with the next instruction in sequence.

#### 2.1.2.8 Sequence of Operations for Operand Phrases

The following sequence of operations is used to process operand phrases:

- I. For the operator phrase of any imprimitive instruction:

- If REPLACEMENT, ADDITION, or CONDITIONAL SUBTRACTION is specified, it is performed on the specified pointer value.

Note: Slashing operations specified for an <u>operator</u> phrase will be ignored.

- II. For each operand phrase:

- Preslash. If the preslash bit is 'l', a copy of the specified pointer is pushed into its associated pointer stack.

- 2.1 Short Phrase. If the Indirect addressing bit is 'l', the specified pointer value is modified (REPLACEMENT) by the halfword modifier in core.

- 2.2 Long Phrase. If REPLACEMENT, ADDITION, or CONDITIONAL SUBTRACTION is specified, it is performed on the specified pointer value.

- III. For each instruction (following the prescan):

- 1.1 If CONDITIONAL SUBTRACTION was not attempted, the instruction

is executed.

- 1.2 If CONDITIONAL SUBTRACTION was attempted, the CS indicator is reset to the 'OR' of the results of the individually attempted CS's.

- 1.2.1 If no CS failed, the instruction is executed.

- 1.2.2 If any phrase failed CS, no name changing or transfer of control occurs and any modifications performed on PR<sub>0</sub> are cancelled. For CALL and EXECUTE processing of the imprimitive continues with the past-scan.

- IV. For each operand phrase:

- 1. Postslash. If the postslash bit is 'l', the pointer at the top of the specified stack is popped out.

- V. After all operand phrases have been considered for postoperations, control is passed to the location designated by PR<sub>0</sub>. If there was a CONDITIONAL SUBTRACTION failure, the new location will be that of the next instruction in core.

Section 2.1.2.8 - 2/2

#### 2.2 Instructions Executed by the Taxicrinic Processors

By definition all Illiac III instructions are initially interpreted by a Taxicrinic Processor. The instructions described in this section are, however, restricted to those whose execution is performed entirely by a TP. This set includes instructions for data transfer, operand stack modification, logical/shift operations, fixed point addition/subtraction and assorted supervisor actions.

#### 2.2.1 Single Cycle Data Transfers

2.2.1.1 Assign

ASSIGN

# 0,0,0,0,0,0 F,D

<0perand $>_{D}^{Imm} <0$ perand $>_{S}^{Imm}$

This two operand instruction may be used to transfer data of variable field length to the address specified by the 'Destination' phrase (to the pointer itself if the Immediate option was specified) from the address specified by the 'Source' phrase (from the pointer register itself if the Immediate option has been specified.)

NOTE: Since the length of the instruction is restricted to at most 5 bytes, <u>both operand phrases</u> <u>cannot be long</u>. However, either or both may be short.

By use of the Immediate option, the following transfers may be obtained:

Destination Source Immediate = '0'. Immediate = '1'

Immediate = '0'To Core From CoreTo Core From RegisterImmediate = '1'To Register From CoreTo Register From Register

Indicators: bounds overflow, parity check.

Section 2.2.1.1 - 1/1

8/10/70

#### 2.2.1.2 Operand Stack Instructions

This set of (4) single operand instructions provides for moving data between the top of the OS and core memory (or pointer registers, if the Immediate option is specified in the operand phrase). For these instructions, operand address will designate either a core address (Imm = 0) or a program register (Imm = 1). 2.2.1.2.1 Push <Operand> PUSH 0,1,0,0,0,F,D A single operand field is transferred from the operand address to the OS. The Operand Stack Pointer (OSP-PR#13) is incremented by FD. Indicators: bounds overflow, parity check. 2.2.1.2.2 Pop 0 <Operand> 0 1 0 0 1 0 F D POP A single operand field is transferred from the OS to the operand address. The ØSP is decremented by FD. Indicators: bounds overflow, parity check. 2.2.1.2.3 Load <Operand><sup>Imm</sup><sub>S</sub> Q1, 00, 10, FD LD The OSP is decremented by FD. A 'PUSH' instruction is then executed. (Effectively, the topmost field of size FD in the OS is overwritten by the field at the operand address.) Indicators: bounds overflow, parity check. 2.2.1.2.4 Store <Operand>\_\_\_\_ ST 01001F.D A 'POP' instruction is executed; the OSP is then incremented by FD. The OS is unchanged. (Effectively, the top FD cell in the OS is duplicated at the operand address.) Indicators: bounds overflow, parity check.

| 2.2.1.3 Mask        | ted Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2.1.3.1 <u>Se</u> | et 🖸 Imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SE                  | T 0,1,0,1,0,0,F,D <operand>_D mm</operand>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                     | The topmost FD field in the OS is treated as a mask.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | Each bit of the mask which is 'l' defines a corresponding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | bit in the field at the operand address which is to be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     | set to 'l'. Bits in positions of the operand field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                     | which correspond to zeros in the mask are unchanged.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | The OS is not changed. (Effectively, an 'OR' between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | the mask and operand field is performed.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | Indicators: bounds overflow, parity check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2.1.3.2 <u>Re</u> | SET O COperand>Imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RE                  | SET 0,1,0,1,0,1, F, D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |